# ANALOG FRONT-ENDS FOR SOFTWARE-DEFINED RADIO RECEIVERS

Samenstelling promotiecommissie:

voorzitter: prof.dr.ir. A.J. Mouthaan Universiteit Twente prof.dr.ir. A.J. Mouthaan secretaris: Universiteit Twente prof.dr.ir. B. Nauta Universiteit Twente promotor: assistent-promotor: dr.ing. E.A.M. Klumperink Universiteit Twente prof.dr.ir. P.G.M. Baltus leden: TU Eindhoven prof.dr.ir. J.C. Haartsen

prof.dr.ir. J.C. Haartsen Universiteit Twente prof.dr.ir. C.H. Slump Universiteit Twente Universiteit Twente Universiteit Twente

© 2007, Vincent Arkesteijn All rights reserved.

ISBN 978-90-365-2562-6 ISSN 1381-3617 (CTIT Ph.D.-thesis series No. 07-101)

This research is supported by the Program for Research on Embedded Systems & Software (PROGRESS) of the Dutch organization for Scientific Research NWO, the Dutch Ministry of Economic Affairs and the technology foundation STW, under grant number 05177.

# ANALOG FRONT-ENDS FOR SOFTWARE-DEFINED RADIO RECEIVERS

#### PROEFSCHRIFT

ter verkrijging van de graad van doctor aan de Universiteit Twente, op gezag van de rector magnificus, prof.dr. W.H.M. Zijm, volgens besluit van het College voor Promoties in het openbaar te verdedigen op vrijdag 14 september 2007 om 16.45 uur

door

Vincent Jan Arkesteijn geboren op 2 juli 1975 te Rotterdam Dit proefschrift is goedgekeurd door

de promotor prof.dr.ir. B. Nauta

de assistent-promotor dr.ing. E.A.M. Klumperink

## **Contents**

| 1 | Intr | duction 1                                 |  |  |  |  |  |  |

|---|------|-------------------------------------------|--|--|--|--|--|--|

|   | 1.1  | Motivation                                |  |  |  |  |  |  |

|   | 1.2  | Software (Defined) Radio                  |  |  |  |  |  |  |

|   | 1.3  | Project description                       |  |  |  |  |  |  |

|   | 1.4  | Previous work                             |  |  |  |  |  |  |

|   | 1.5  | Thesis Outline                            |  |  |  |  |  |  |

| 2 | Soft | vare Radio 7                              |  |  |  |  |  |  |

|   | 2.1  | Sampler-based architectures               |  |  |  |  |  |  |

|   |      | 2.1.1 Software Radio                      |  |  |  |  |  |  |

|   |      | 2.1.2 Direct RF Sampling                  |  |  |  |  |  |  |

|   | 2.2  | Requirements                              |  |  |  |  |  |  |

|   |      | 2.2.1 Sample rate                         |  |  |  |  |  |  |

|   |      | 2.2.2 SNR 10                              |  |  |  |  |  |  |

|   |      | 2.2.3 Jitter                              |  |  |  |  |  |  |

|   |      | 2.2.4 SFDR                                |  |  |  |  |  |  |

|   | 2.3  | Feasibility                               |  |  |  |  |  |  |

|   | 2.4  | Summary and Conclusions                   |  |  |  |  |  |  |

| 3 | Soft | vare Defined Radio 25                     |  |  |  |  |  |  |

|   | 3.1  | Downconverter without RF pre-filtering 26 |  |  |  |  |  |  |

|   |      | 3.1.1 Noise requirement                   |  |  |  |  |  |  |

|   |      | 3.1.2 Linearity requirement               |  |  |  |  |  |  |

|   |      | 3.1.3 Conclusion                          |  |  |  |  |  |  |

|   | 3.2  | Downconverter with RF pre-filtering       |  |  |  |  |  |  |

|   |      | 3.2.1 Linearity requirement               |  |  |  |  |  |  |

|   |      | 3.2.2 Selection of intermediate frequency |  |  |  |  |  |  |

|   | 3.3  | RF Filtering                              |  |  |  |  |  |  |

|   | 3.4  | Local Oscillator                          |  |  |  |  |  |  |

|    |       | 3.4.1 Jitter                                         | 45       |

|----|-------|------------------------------------------------------|----------|

|    |       | 3.4.2 Sampling and mixing compared                   | 46       |

|    | 3.5   | Channel filtering and analogue-to-digital conversion | 48       |

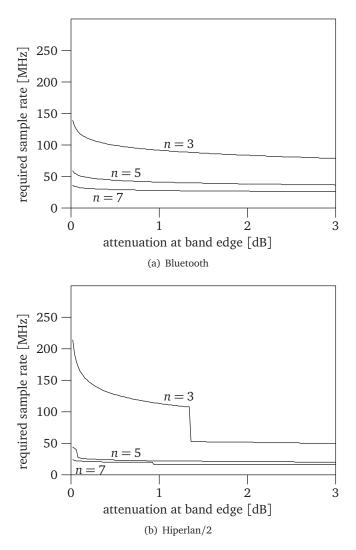

|    |       | 3.5.1 Sample rate                                    | 50       |

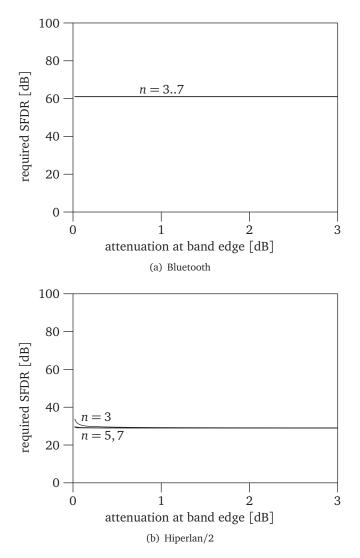

|    |       | 3.5.2 SFDR                                           | 50       |

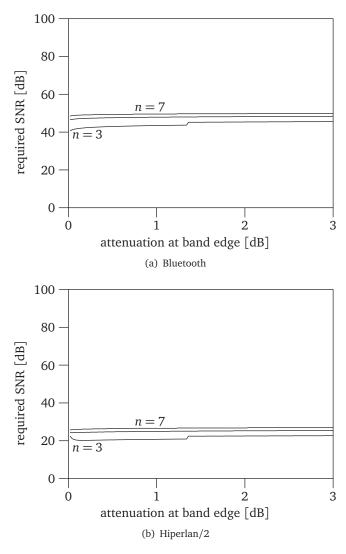

|    |       | 3.5.3 SNR                                            | 52       |

|    |       | 3.5.4 Resolution                                     | 52       |

|    |       | 3.5.5 Variable gain                                  | 55       |

|    |       | 3.5.6 Conclusion                                     | 57       |

|    | 3.6   | Summary and conclusions                              | 57       |

| 4  | A wi  | deband downconverter                                 | 59       |

| •  | 4.1   | Design considerations                                | 60       |

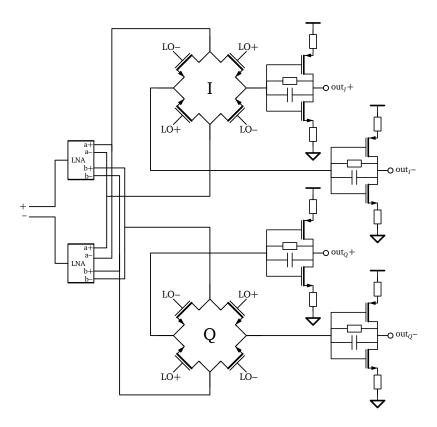

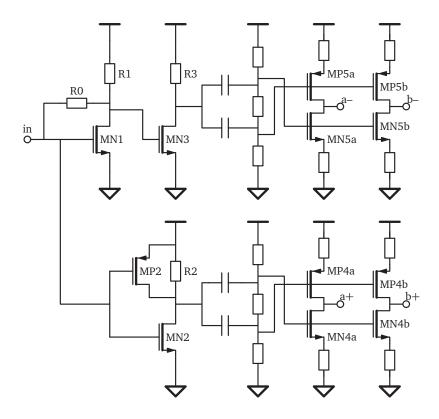

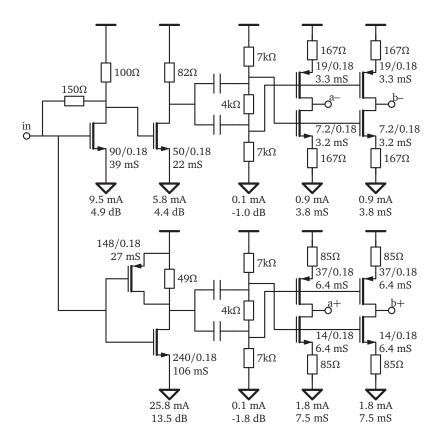

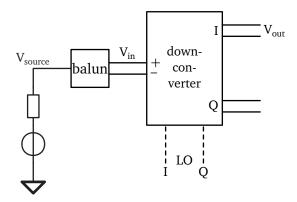

|    | 4.2   | Circuit overview                                     | 61       |

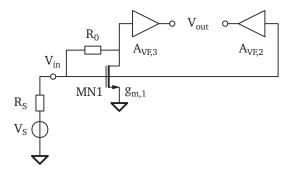

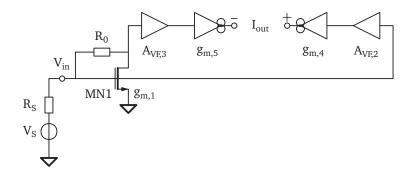

|    | 4.3   | Low-Noise Amplifier                                  | 61       |

|    | 4.4   | Mixer                                                | 67       |

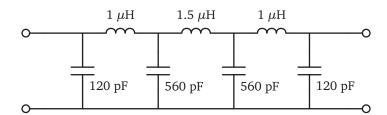

|    | 4.5   | IF filter and amplifier                              | 69       |

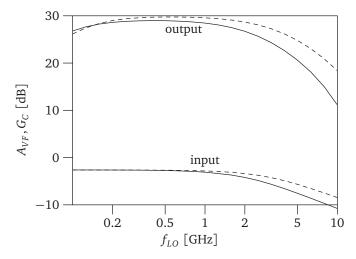

|    | 4.6   | Simulations                                          | 69       |

|    | 4.7   | Measurements                                         | 71       |

|    | 4.8   |                                                      | 71<br>79 |

|    | 4.0   | Combination with postprocessing                      | 79<br>79 |

|    |       | 4.8.1 Software                                       |          |

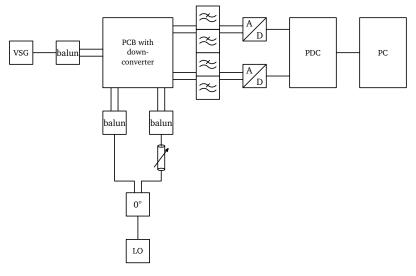

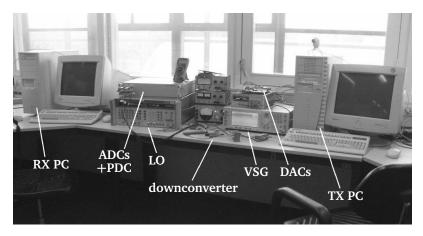

|    |       | 4.8.2 Hardware                                       | 80       |

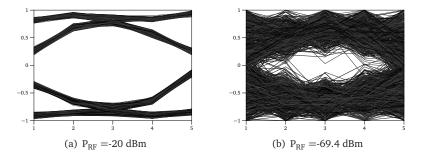

|    | 4.0   | 4.8.3 Experimental results                           | 84       |

|    | 4.9   | Conclusions                                          | 86       |

|    | 4.10  | Discussion                                           | 87       |

| 5  | Sum   | mary and conclusions                                 | 91       |

|    | 5.1   | Summary                                              | 91       |

|    | 5.2   | Conclusions                                          | 92       |

|    | 5.3   | Recommendations for further research                 | 92       |

| Sa | menv  | atting                                               | 93       |

| Da | ınkwo | oord                                                 | 95       |

| ٨  | Into  | modulation distortion                                | 97       |

| A  |       |                                                      |          |

|    | A.1   | Frequencies                                          | 97       |

|    |       | A.1.1 Second order                                   | 97       |

|    |       | A.1.2 Third order                                    | 98       |

|    | AΊ    | Levels                                               | 98       |

| Bibliography         | 101 |

|----------------------|-----|

| List of publications | 107 |

## Chapter 1

## Introduction

#### 1.1 Motivation

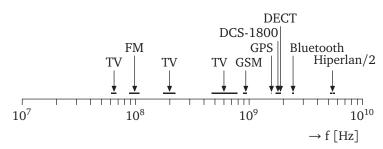

After its introduction in the late 19<sup>th</sup> century, radio communication has seen increasing use. Not only its use has increased, but also the number of modulation formats and the frequency range that is being used. In recent years, the proliferation of radio standards has progressed even faster. This has lead to a plethora of standards, such as GSM and WCDMA for cellular communication, Hiperlan/2 and IEEE 802.11a/b/g for wireless networking, and many more. All these standards have different modulation types, bandwidths, and carrier frequencies. For illustration, figure 1.1 shows the frequency bands that some of these standards use.

The increasing number of standards leads to an increasing number of different radios, which is unwieldy for both manufacturers and con-

Figure 1.1: part of the available radio spectrum and some commercially relevant uses thereof

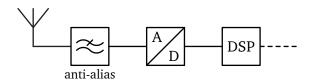

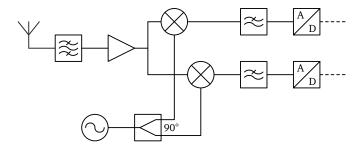

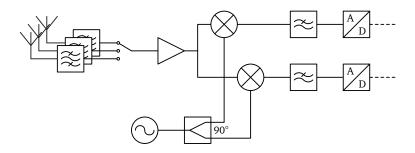

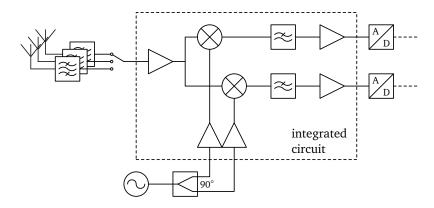

Figure 1.2: an example of a software radio receiver front-end

sumers. Manufacturers need to spread their R&D efforts on a large set of hardware platforms. Furthermore, they need to manufacture, stock and distribtute many different radios. Consumers need to buy and carry a different radio for every application they expect to use, and often some more if they intend to visit other regions.

A solution would be a more flexible, reconfigurable radio, which can support many different standards. Such a radio would also have advantages in dynamic environments, where it can adapt to for instance varying channel parameters, or varying levels of interferers.

#### 1.2 Software (Defined) Radio

The holy grail of flexible radio receivers is the 'Software Radio', sometimes also referred to as 'Ideal' or 'True' Software Radio. As its name suggests, all of the radio functionality –such as channel selection and demodulation– is implemented in software. This form was described by Mitola in [1]. Assuming that software is flexible or at least replaceable, this approach yields a flexible receiver.

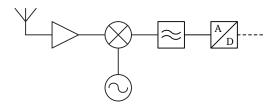

Software runs on digital hardware, and because signals at the antenna interface are analogue, an analogue-to-digital converter (ADC) has to be included as well. A general block schematic of a software radio receiver front-end is shown in figure 1.2.

As will be shown in chapter 2, a true software radio is hard to implement and will likely remain utopian for some time to come. A solution that is more feasible in the near future is a radio receiver where part of the flexibility is achieved by flexible analogue hardware instead of by software. This is called a 'Software Defined Radio' (SDR). Another way to view this is that an analogue front-end conditions the antenna signal before it is converted to digital.

#### 1.3 Project description

The research described in this dissertation was performed within the project 'Development of a software-radio based embedded mobile terminal'. The goal was to assess feasibility of and develop a mobile software-defined radio terminal. This should lead to a radio which can support multiple standards, and which can easily be updated when the need arises.

The scope was further limited to a receiver, and specifically to the parts of the receiver starting directly after the antenna and up to the demodulator.

This dissertation describes the research into the part of the receiver up to and including the ADC. The research on the digital part of the receiver, which mostly covers channel selection and demodulation, is described in Roel Schiphorst's dissertation [2].

The term 'mobile terminal' covers many types of devices, from a cellular phone to a vehicle-based transceiver. Because power constraints in a cellular phone or a PDA are likely too limiting for a software-defined radio approach, a laptop was chosen as a platform. Not only is more power available, but laptops already have a fast processor, which can be used for software radio signal processing.

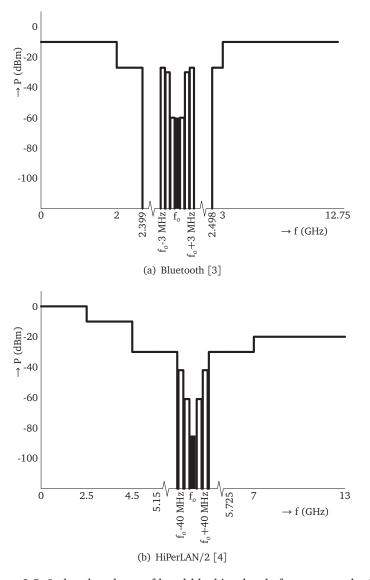

As stated earlier, the aim is to design and analyze receivers capable of receiving signals of *any* standard. This is a very broad goal, and therefore the scope has been limited further by selecting two specific but very different standards. These are Bluetooth [3] and Hiperlan/2 [4]. As can be seen in table 1.1, these standards have very different parameters. Hopefully, by choosing two dissimilar standards, not too much generality will be lost and conclusions drawn from experiments with these two standards can be generalised to a larger class of problems. Most importantly, the used frequency bands are quite far apart. This is also shown in figure 1.1.

Yet another choice to be made is the implementation technology. Although technologically advanced processes such as BiCMOS, GaAs, SiGe have clear advantages, especially at higher frequencies, this dissertation focuses on CMOS. First, this is because of advantages such as low cost, portability between fabs, et cetera that are common to most applications. More important in the context of a software defined radio receiver however, is the possiblity of monolithic integration with the digital parts

|                                      | Bluetooth | Hiperlan/2              |

|--------------------------------------|-----------|-------------------------|

| frequency band [GHz]                 | 2.4-2.48  | 5.15-5.725 <sup>1</sup> |

| channel bandwidth <sup>2</sup> [MHz] | ~0.6      | 16                      |

| channel spacing [MHz]                | 1         | 20                      |

| nominal bit rate [Mb/s]              | 1         | 6–54                    |

| modulation type                      | GFSK      | QAM + OFDM              |

| multiple access scheme               | FHSS      | TDMA                    |

| duplex scheme                        | TDD       | TDD                     |

Table 1.1: key characteristics of Bluetooth [3] and Hiperlan/2[4]

of the receiver.

#### 1.4 Previous work

Naturally, design of radio receivers is as old as radio itself. Although early radio receivers didn't have much selectivity and therefore could be considered wideband, they are not very useful on the present crowded radio spectrum.

Software (defined) radio receivers are a more recent phenomenon. However, at the start of our project already much research has been done in the area. Many projects investigated the software needed for software defined radio, while some had researched the flexible digital hardware needed, e.g. [5].

Few however, included RF hardware in their research. One software radio is described in [6]. In this HF transceiver, the entire spectrum from 0 to 31 MHz is digitised. Another project is the military Speakeasy project [7, 8], where the objective is to cover the entire band from 2 MHz to 2 GHz.

A software defined radio at higher frequencies is described in [9]. Here, signals in both the 1.5 and 1.9 GHz bands are downconverted and digitised. Some other projects had started, like SUNBEAM, SODERA, PROMURA and FIRST. However, no tangible results were available

To the best of our knowledge, no CMOS integrated software-defined radio receivers had been published at the start of this research in September 2000.

<sup>&</sup>lt;sup>1</sup>with a gap between between 5.35 and 5.47 GHz

<sup>&</sup>lt;sup>2</sup>Many definitions of bandwidth exist and these numbers are not meant to define the bandwidth exactly, but merely to illustrate the difference between the two standards.

#### 1.5 Thesis Outline

After the introduction in this chapter, chapter 2 discusses software radio. The ADC requirements will be derived, with most attention to sampling clock jitter requirements.

In chapter 3, software defined radio is discussed. Front-end requirements such as noise figure and intermodulation intercept points will be derived in relation to the amount of RF pre-filtering. This way, a trade-off can be made. Furthermore, requirements on the IF ADC will be derived in relation to the amount of IF filtering.

In chapter 4, the design of a wideband integrated downconverter is discussed. The design has been realised in 0.18  $\mu$ m CMOS. In addition to measurement results of the downconverter, test results of the downconverter in combination with digital channel selection and demodulation are presented.

And finally, chapter 5 summarizes the conclusions, discusses the results and gives recommendations for further research.

## Chapter 2

## **Software Radio**

As software is flexible or at least replaceable, a receiver architecture where all signal processing is done in software, will yield much flexibility. A highly digital CMOS receiver implementation also has all the advantages of digital design (easier/faster development, benefits from Moore's law, easy porting to newer technology). Therefore, such an architecture, called 'software radio' seems very attractive. It will be discussed in this chapter.

In addition to this software radio, another architecture, also employing direct RF sampling but without amplitude quantisation will be discussed. This is mainly done because many of its properties and requirements correspond to those of the software radio architecture.

The question that this chapter tries to answer is whether these architectures are feasible given today's available technology. Therefore, after introducing the architectures, requirements on their implementations will be discussed. These requirements are calculated for a receiver capable of receiving both Bluetooth and Hiperlan/2. Finally these requirements are compared to the performance of currently available components and from this conclusions are drawn.

### 2.1 Sampler-based architectures

This section introduces the two architectures discussed in this chapter.

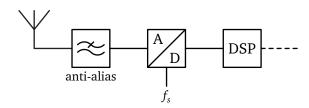

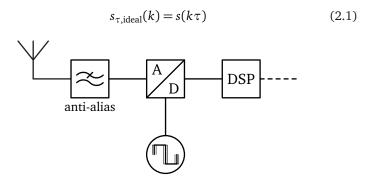

Figure 2.1: architecture of a software radio receiver front-end

#### 2.1.1 Software Radio

A true software radio front-end is shown in figure 2.1. The incoming signal is first filtered by a lowpass filter. The filter's only function in this architecture is anti-aliasing, so all signals up to the filter's cut-off frequency will be present at the ADC input.

After filtering, the signal is sampled and quantised by the ADC. To avoid aliasing, the sample rate  $f_s$  is higher than twice the filter's cut-off frequency. All further processing is done on some kind of programmable digital hardware, here indicated with 'DSP' The programmability of this digital hardware yields the desired flexibility.

The ADC in this diagram is the block whose requirements and feasibility will be discussed in this chapter.

The anti-alias filter in this receiver will be assumed to be a brickwall filter. This cannot be realized, so in practice the requirements on the ADC will be even higher than calculated here.

The requirements on and feasibility of the digital hardware are outside the scope of this thesis, but are discussed in [2] instead.

#### 2.1.2 Direct RF Sampling

Another architecture, which was recently proposed [10] also employs direct RF sampling, but without amplitude quantisation. Another difference with the architecture in the previous section, is that here the sample rate  $f_s$  is ususally equal to the frequency of the wanted signal  $f_{RF}$ . This way, the signal is downconverted by the sampling process. In that respect it is comparable to a zero-IF receiver, but here the RF signal is sampled, and subsequent processing is done in discrete time.

This architecture scales well to smaller processes. One reason to mention this architecture is its potential flexibility [11]. However, present

implementations of this architecture don't give very flexible radio receivers. Some reasons for this are given in [12].

From that perspective, this architecture does not fit in very well with this chapter. However, part of the requirements that will be derived in the next section are equally valid for this architecture. The fact that RF sampling receivers are feasible therefore implies that at least some of the requirements for software radio receivers can be met. Note however, that these receivers are preceded by a bandpass filter, which greatly relaxes some of the requirements.

#### 2.2 Requirements

When implementing the above architectures, limited performance of the building blocks limits receiver performance. Minimum performance requirements therefore impose (combined) requirements on these building blocks. This section discusses the most important requirements for the software radio architecture of figure 2.1.

To assess the feasibility of a software radio receiver, all the requirements will be calculated. This will be done for a receiver capable of receiving both Bluetooth and Hiperlan/2, as described in section 1.3.

Of the requirements, most attention is given to jitter (section 2.2.3). Most of that section was previously published in  $\lceil 13 \rceil$  and  $\lceil 14 \rceil$ .

#### 2.2.1 Sample rate

According to the Nyquist-Shannon sampling theorem, a signal of finite bandwidth can be reconstructed exactly from its sampled version, if the sampling rate is higher than twice the bandwidth[15]. Our objective is not perfect reconstruction, but merely demodulation and/or detection of one desired signal, so conceivably some other criterion could be found. However, this criterion would depend on the demodulator, which depends on the signal of interest, and in order not to limit the receiver to specific types of signals, the sampling theorem is still assumed to give a necessary condition.

Therefore, assuming a low-pass AD converter, the sampling rate of the receiver should at least equal twice the highest frequency present at the input. Since the cut-off frequency of the anti-alias filter cannot be lower than the maximum signal frequency, this means the sample rate should be at least twice the maximum signal frequency.

#### Example

The maximum frequency of interest for a combined Bluetooth and Hiperlan/2 receiver is 5.725 GHz. Therefore, this will be the cut-off frequency of the anti-alias filter, and the sampling rate should be higher than  $2 \times 5.725 = 11.45$  GHz.

#### 2.2.2 SNR

Signal-to-noise ratio (SNR) can both be a property of a signal and of a system. When used to describe a system, it ususally refers to the maximum SNR of the output signal of the system. This is also the case with analogue-to-digital converters:

Signal-to-noise ratio (SNR) is the ratio of the signal power to the total noise power at the output (usually measured for a sinusoidal input). [16]

As the output signal is digital, power in this context is not physical power, but can be interpreted as signal variance. For deriving this requirement, both the signal power and the maximum allowed total noise power have to be known.

When one strong interferer is present, this dominates the input signal power. Therefore, the maximum input power equals the maximum blocker power within the bandwidth of the filters preceding the ADC.

The noise power at the output of the converter should be low enough not to interfere with demodulation of the signal. Most standards do not specify the maximum noise level, but instead specify the bit (or frame) error rate at some input sensitivity level. Therefore, derivation of the noise floor requires selecting and often simulating a demodulation algorithm. This derivation is outside the scope of this thesis, but results from literature can be used.

#### **Example**

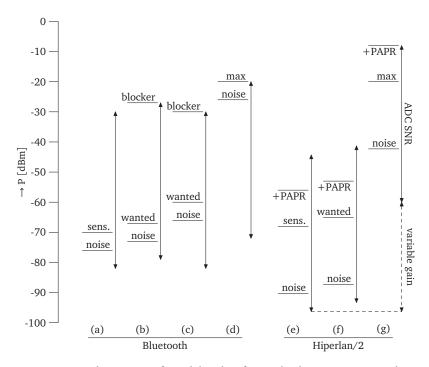

As can be seen in the blocker specification in figure 2.5 on page 18, the maximum input signal is 0 dBm for Hiperlan/2 and -10 dBm for Bluetooth.

Calculating the maximum noise level is somewhat more involved as this is not specified in the standards. For this, both the minimum sensitivity level for which some bit (or frame) error rate is to be achieved, and the SNR at which the demodulator achieves this error rate have to

|                | sensitivity | required<br>in-band | max in-band | noise floor |

|----------------|-------------|---------------------|-------------|-------------|

| standard       | (dBm)       | SNR (dB)            | noise (dBm) | (dBm/Hz)    |

| HL/2 (6 Mb/s)  | -85         | 6.2                 | -91.2       | -163.3      |

| HL/2 (9 Mb/s)  | -83         | 7.4                 | -90.4       | -162.5      |

| HL/2 (12 Mb/s) | -81         | 8.9                 | -89.9       | -162.0      |

| HL/2 (18 Mb/s) | -79         | 10.9                | -89.9       | -162.0      |

| HL/2 (27 Mb/s) | -75         | 14.5                | -89.5       | -161.6      |

| HL/2 (36 Mb/s) | -73         | 17.0                | -90.0       | -162.1      |

| HL/2 (54 Mb/s) | -68         | 22.3                | -90.3       | -162.4      |

|                |             |                     |             |             |

| Bluetooth      | -70         | 18.0                | -88.0       | -148.0      |

Table 2.1: Calculation of the maximum noise floor of the combined receiver, for all (sub-)standards. (Hiperlan/2 is abbreviated as HL/2)

be known. The standards specify the sensitivity level. It is shown in the second column in table 2.1.

The required SNR depends on the demodulator. The demodulator used in conjunction with the front-end described in this thesis, has been described in [2]. The numbers in the third column, 'required in-band SNR' were taken from there. This is the required SNR for the demodulator's input signal, and should not be confused with the ADC's SNR.

The maximum in-band noise (fourth column) is now calculated by subtracting the required SNR from the sensitivity level. The noise floor (fifth column) is the corresponding power spectral density. For this a bandwidth of 1 MHz was used for Bluetooth, and 16.5625 MHz for Hiperlan/2.

The lowest noise floor is for a 6 Mb/s Hiperlan/2 signal: -163.3 dBm/Hz. In the 5.7 GHz bandwidth of the receiver, this corresponds to a total noise of -65.7 dBm.

Therefore, the required SNR for the converter is 0 dBm - .65.7 dBm = 65.7 dB.

To convert this to a resolution, the waveform of the strong out-of-band interferers that dominate the input signal needs to be known. The Bluetooth standard specifies this to be a sine wave. The Hiperlan/2 standard does not specify this, but we will assume the same. Then, we can convert this SNR (in dB) to a number of bits n using  $SNR = 6.02 \cdot n + 1.76$ . Therefore, if we allow all the noise to be caused by quantisation, the required resolution of the converter is 11 bits.

#### 2.2.3 **Jitter**

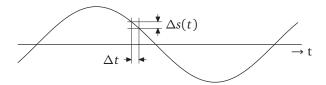

The ADC in the software radio architecture from figure 2.1 requires a clock source, as shown in figure 2.2. Jitter in this sampling clock leads to uncertainty in the sampling instant, and thus to an error in the sampled signal. See figure 2.3.

As will be shown in the section 'white-noise model', according to a commonly used model for white ADC clock jitter [17], the resolution directly affects the clock jitter requirements, resulting in very stringent numbers. Better jitter models are available in the literature, e.g. [18, 19, 20]. Here, the jitter spectrum is still considered white, resulting in a white error spectrum at the output of the ADC. In [21], spectra of input signal and jitter are taken into account, but only the error signal over the full Nyquist bandwidth is considered. For a radio receiver however, only the error signal in the channel bandwidth is relevant. Therefore, [18, 19, 20, 21] yield too pessimistic jitter requirements.

The section 'coloured noise model' will show a model comparable to that in [18, 19, 20, 21]. We show that using this model, taking into account the spectra of both the input signals and the sampling clock jitter, and looking at the jitter-induced error signal only in the frequency band of interest, sampling clock jitter requirements can be relaxed greatly.

#### White noise model

Consider an incoming signal s(t). Ideally, the sampled version of this signal with sample rate  $1/\tau$ ,  $s_{\tau}(k)$ , is constructed as follows.

Figure 2.2: architecture of a software radio receiver front-end, with sampling clock source

Figure 2.3: An input signal as a function of time and the effect of sampling jitter

Due to sampling jitter however, an error will be introduced, as can be seen in figure 2.3. The sampled signal can now be calculated as follows (for small absolute jitter  $\Delta t$ ).

$$s_{\tau}(k) = s(k\tau + \Delta t(k\tau))$$

$$\approx s(k\tau) + \underbrace{\Delta t(k\tau) \cdot \frac{\partial}{\partial t} s(t)}_{\Delta s_{\tau}(k)}$$

(2.2)

This signal consists of a sampled version of the input signal s(t) plus an error signal  $\Delta s_{\tau}(k)$  due to jitter. When requiring the RMS value of  $\Delta s_{\tau}(k)$  to be lower than the RMS error due to quantisation, the following relation between required RMS jitter (the RMS value of the absolute jitter  $\Delta t(k\tau)$ ) and resolution can be derived [22].

$$\Delta t_{rms} = \frac{2^{-n}}{\pi f_{max} \sqrt{6}} \tag{2.3}$$

Here, a full swing harmonic input signal at the maximum input frequency  $f_{max}$  is assumed. n is the resolution of the ADC.

Using this equation, the required RMS jitter can be calculated for a given resolution. For software radio applications this yields clock jitter requirements that are not achievable with currently available (integrated) clock sources, as will be shown in the comparison later on.

#### Coloured noise model

The preceding analysis only derives the RMS value of the jitter induced error. This is often sufficient, especially when the signals of interest are wideband. In the case of a software radio receiver however, only a narrow portion of the converted bandwidth is of interest, and the spectral distribution of the error signal  $\Delta s_{\tau}(k)$  becomes relevant.

To derive the spectrum of the error signal, consider the following. As seen in equation 2.2, the error signal  $\Delta s_{\tau}(k)$  is the time derivative of the input signal  $\frac{\partial}{\partial t}s(t)$  multiplied with the sampling time error  $\Delta t(k\tau)$ :

$$\Delta s_{\tau}(k) = s(k\tau + \Delta t(k\tau)) - s(k\tau)$$

$$\approx \Delta t(k\tau) \cdot \frac{\partial}{\partial t} s(t) \Big|_{k\tau}$$

(2.4)

Taking the discrete-time Fourier transform (DTFT) of both sides:

$$\mathscr{F}(\Delta s_{\tau}(k)) \approx \mathscr{F}(\Delta t(k\tau)) * \mathscr{F}\left(\left.\frac{\partial}{\partial t}s(t)\right|_{k\tau}\right)$$

(2.5)

where  $\mathscr{F}$  denotes the DTFT and \* denotes convolution. This result is also obtained in [18, 23]. Apparently, for calculating the spectrum of the error signal, both the input signal and the spectrum of the jitter have to be known.

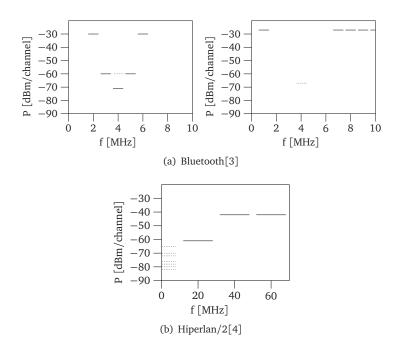

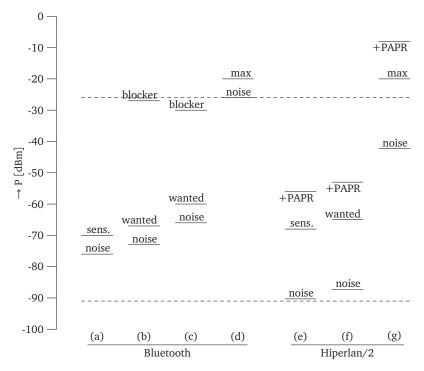

The input spectrum of a radio receiver is not known in general, but wireless communication standards normally limit the power levels of interfering signals that have to be tolerated at different frequencies. Figure 2.5 shows the blocking levels for Bluetooth [3] and Hiperlan/2 [4]. These blocking levels form an upper limit to the input signal s(t). From this power spectrum, an upper limit to  $\frac{\partial}{\partial t}s(t)$  can be calculated by multiplying the corresponding amplitudes by  $j\omega$ . Note that interfering signals that are close in frequency to the wanted signal have far lower maximum power levels than those further away. We will see later that this greatly relaxes phase noise requirements.

Furthermore, the spectrum of  $\Delta t(t)$  has to be known. When the sampling clock is derived from a synthesizer containing a VCO (e.g. an LC or ring oscillator),  $\Delta t(t)$  can be assumed to have a  $f^{-2}$  power spectrum outside the synthesizer loop bandwidth [24]. An example of such a spectrum can be seen in figure 2.7. Above the synthesizer loop bandwidth (which is 100 kHz in this example), the phase noise of the synthesizer is dominated by that of the VCO.

Also, because variance of the absolute jitter at the output of a first or second-order PLL is constant when the observation time exceeds the loop time constant [25], the jitter process is assumed to be stationary.

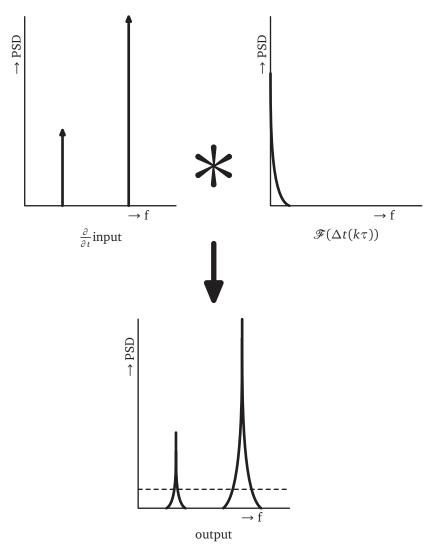

The effect of applying equation 2.5 to the input and jitter spectra described above can best be illustrated with the example of an interfering

harmonic input signal  $s(t) = A_i \sin(\omega_i t)$ :

$$\mathcal{F}(\Delta s_{\tau}(k)) \approx \mathcal{F}(\Delta t(k\tau)) * \mathcal{F}\left(\frac{\partial}{\partial t} A_{i} \sin(\omega_{i} t) \Big|_{k\tau}\right)$$

$$= \mathcal{F}(\Delta t(k\tau)) * \omega_{i} A_{i} \cdot \mathcal{F}\left(\cos(\omega_{i} k\tau)\right) \qquad (2.6)$$

Due to its  $f^{-2}$  nature, most energy in  $\Delta t(k\tau)$  is at low frequencies. Knowing that in the frequency domain this is convolved with the derivative of the input signal leads to the following.

- 1. The convolution operation in equation 2.5 shifts the jitter spectrum  $\mathscr{F}(\Delta t(k\tau))$  to the frequencies of input signals. Therefore, the jitter-induced error in the output is concentrated around these frequencies.

- Input signals with higher power are surrounded by more jitterinduced error in the output than input signals with lower power, due to the linearity of the convolution operation.

- 3. Input signals of higher frequencies are surrounded by more jitter-induced error in the output than signals at lower frequencies, because of the frequency dependent effect of  $\frac{\delta}{\delta t}s(t)$ . This is in accordance with the results in [20].

The above is illustrated in figure 2.4. There, the effects described under 1 and 2 are clearly visible: the jitter-induced error in the output is concentrated around the input frequencies, and it has more power around input signals with higher power. To compare the jitter-induced error spectrum with the one predicted by a white-noise model, a flat line has been drawn, indicating a white spectrum with the same RMS value as the actual (coloured) noise spectrum.

Because the jitter-induced output error is concentrated around the frequencies with the strongest input signals, it is less of a problem in the frequency band of interest. This is further illustrated in the example of the next section.

#### Comparison

To illustrate the significance of the difference between the two ADC models, a numeric example will be given.

The combined receiver for Bluetooth and Hiperlan/2 requires a bandwidth of 6 GHz and a resolution of 11 bits (sections 2.2.1 and 2.2.2).

Figure 2.4: Illustration of equation 2.6. The convolution of the input spectrum (upper left) with the spectrum of  $\Delta t(k\tau)$  (upper right) gives the output spectrum of the ADC (bottom). For comparison purposes, the dashed line represents a white error spectrum with the same RMS value as the actual spectrum.

Using these numbers in equation 2.3 results in

$$\Delta t_{rms} = \frac{2^{-11}}{\pi \cdot 6G \cdot \sqrt{6}} \approx 11 \text{ [fs]}$$

This is one or two orders of magnitude smaller than what is achieved by currently published integrated synthesizers. For instance, a state-of-the-art system as described in [26] reports 0.22 ps RMS jitter.

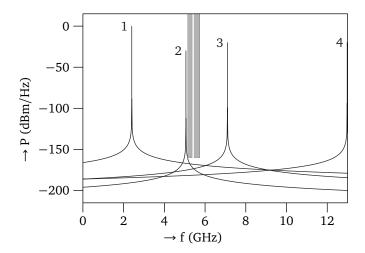

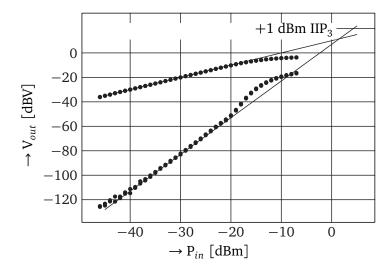

If we use the more realistic ADC model however, results are different. Figure 2.6 shows the output spectrum of an ADC, with four different interfering input signals. The levels of these signals were taken to be the blocking levels as shown in figure 2.5, at the frequencies where their impact is most severe (2.4, 5.06, 7.1 and 12.98 GHz). None of these interferers cause the jitter-induced output error to exceed the maximum allowed in-band noise level (indicated by the shaded area).

To improve readability of this figure, in-band interferers have been left out. Further analysis showed that the jitter-induced error due to in-band interferers is just below the maximum in-band noise level.

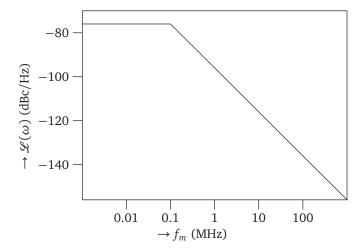

The RMS jitter of the 12 GHz sampling clock used for figure 2.6 was 1.3 ps, with a flat power spectrum up to 100 kHz from the carrier and a  $f^{-2}$  roll-off above that. This corresponds to -96 dBc/Hz phase noise at 1 MHz offset. These values have been chosen to just comply with in-band noise requirements. This spectrum is shown in figure 2.7.

To assess the feasibility of an oscillator with this phase noise performance, the 'oscillator number' figure of merit (FoM) as defined in [27] as

$$FOM_{Osc-No} = 10 \log(\mathcal{L}(f_m)) + 20 \log\left(\frac{f_m}{f_{osc}}\right)$$

For the numbers given above:

$$FOM_{Osc-No} = -96 + 20 \log \left( \frac{1MHz}{12GHz} \right) = -176$$

In [27], numbers well under -190 are reported for CMOS integrated oscillators, so the required jitter appears feasible.

It is clear from figure 2.6 that the strongest signal (0 dBm at 2.4 GHz), which was the limiting factor in the first model, does not form a key factor in the second model. This shows that the more realistic model yields far more feasible requirements than the first model (1.3 ps absolute RMS jitter instead of 11 fs).

Figure 2.5: In-band and out-of-band blocking levels for two standards, together with level of the wanted signal (solid bar at  $f_0$ ) during blocking tests. Note: frequency axes are not to scale.

Figure 2.6: ADC output signal (input referred) for four demanding interfering input signals (0 dBm @2.5 GHz, -30 dBm @5.15 GHz, -20 dBm @7 GHz and -20 dBm @13 GHz). Acceptable reception requires the in-band jitter-induced output noise to be below the shaded area. This area is delimited by the band limits (5150-5350 and 5470-5725 MHz) and the maximum acceptable in-band noise level for both Hiperlan/2 bands.

#### Maximum jitter spectrum

Until here, the effects of jitter on sampling were analysed, in the context of a software radio receiver. In this section, the converse of this analysis will be discussed. Given the input blockers and a maximum allowed in-band noise level, an upper limit to the jitter spectrum will be derived.

The convolution operation in equation 2.6 shifts the jitter spectrum  $\mathscr{F}(\Delta t(k\tau))$  by the frequency of the interferer. Evaluating the jitter-induced output error at the frequency of the wanted signal  $\omega_w$  therefore yields

$$\mathscr{F}(\Delta s_{\tau}(k))\big|_{\omega_{w}} \approx \omega_{i} A_{i} \cdot \mathscr{F}(\Delta t(k\tau))\big|_{|\omega_{w}-\omega_{i}|}$$

(2.7)

Since both an interferer at  $\omega_i - \omega_w$  above the wanted signal and an interferer at  $\omega_w - \omega_i$  below the wanted signal can be shifted to the frequency of the wanted signal, the absolute value of this frequency difference is taken. Also, because  $\Delta t(k\tau)$  is real,  $\mathscr{F}(\Delta t(k\tau))|_{\omega_m}$  is a symmetrical function.

Figure 2.7: Phase noise spectrum of the 12 GHz clock used for the example in figure 2.6.

If we take the PSD  $S_{\Delta s_{z}}(\omega_{w})$  of the error signal,

$$S_{\Delta s_{\tau}}(\omega_{w}) \approx \omega_{i}^{2} P_{i} \cdot S_{\Delta t}(|\omega_{w} - \omega_{i}|)$$

$$= \omega_{i}^{2} P_{i} \cdot \frac{1}{\omega_{CLK}^{2}} S_{\Phi}(|\omega_{w} - \omega_{i}|) \qquad (2.8)$$

Here,  $\omega_{\rm CLK}$  is the clock frequency,  $S_{\Phi}$  is the PSD of the phase error and  $S_{\Delta t} = \frac{1}{\omega_{\rm CLK}^2} S_{\Phi}$  is the PSD of the time error.

This error signal should be lower than the maximum allowed inband noise density,  $N_{\text{max}}$ . With  $P_{i,max}(\omega_i)$  the maximum input power at a certain frequency (the blocker profile),

$$\omega_i^2 P_{i,\text{max}}(\omega_i) \cdot \frac{S_{\Phi}(|\omega_w - \omega_i|)}{\omega_{\text{CLK}}^2} < N_{\text{max}}$$

(2.9)

$$\omega_{\text{CLK}}^{2}$$

$$S_{\Phi}(|\omega_{w} - \omega_{i}|) < \frac{N_{\text{max}}\omega_{\text{CLK}}^{2}}{\omega_{i}^{2}P_{i,\text{max}}(\omega_{i})}. \tag{2.10}$$

This can be rewritten as the following set of upper bounds on the phase noise spectrum, with  $\omega_m = |\omega_w - \omega_i|$  the modulation frequency of the

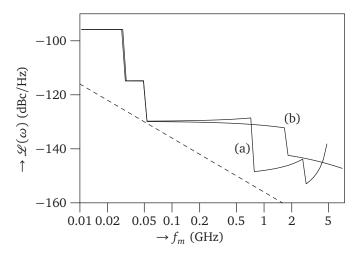

Figure 2.8: An upper bound on the phase noise spectrum for the 12 GHz sampling clock of a software radio receiver capable of receiving Hiperlan/2, calculated using equation 2.11. The labels (a) and (b) correspond to those in equation 2.11. The phase noise spectrum should be below *both* lines. The dashed line represents  $1/f^2$  phase noise of -96 dBc/Hz at 1 MHz offset, just complying with the requirements.

jitter component.

$$\begin{cases} S_{\Phi}(\omega_m) & < \frac{N_{\max}\omega_{\text{CLK}}^2}{(\omega_w - \omega_m)^2 P_{i,\max}(\omega_w - \omega_m)} \\ \\ S_{\Phi}(\omega_m) & < \frac{N_{\max}\omega_{\text{CLK}}^2}{(\omega_w + \omega_m)^2 P_{i,\max}(\omega_w + \omega_m)} \end{cases}$$

(a)

There are two bounds, labeled (a) and (b). These correspond to the two sides of the wanted signal where an interferer might be found.

#### Example

This upper bound has been calculated for the same receiver as used in the previous section. The result can be seen in figure 2.8, where  $\mathscr{L}(\omega_m)=\frac{1}{2}S_\Phi(\omega_m)$ . Because both the inequalities of equation 2.11 should be satisfied,  $\mathscr{L}(\omega_m)$  should be below both lines.

The steps in the curve correspond to the steps in the blocker profile of figure 2.5. The deviation from horizontal lines is due to the  $(\omega_w \pm \omega_m)$  factor in equation 2.11.

One phase noise spectrum that conforms to these requirements, is a  $1/f^2$  spectrum with -96 dBc/Hz at 1 MHz offset. This is indicated by the dashed line in figure 2.8. One thing to note is the sharp rise towards 5.5 GHz, corresponding to the frequency of the wanted input signal. Jitter at this frequency will convolve with a DC input to the wanted output frequency. As jitter has no effect on sampling a DC signal (its derivative is zero), the jitter spectrum may be arbitrarily high at that frequency.

#### **Conclusions**

When judging the effect of clock jitter on the output of samplers over the entire frequency range, knowledge of only the RMS value of the time jitter, combined with knowledge of amplitude and maximum frequency of the input signal is sufficient. When one is only interested in a narrow portion of the bandwidth of the sampled signal, as in a software radio receiver, the same approach yields overly stringent requirements on the clock jitter.

Combining knowledge of the jitter spectrum with knowledge of the spectrum of the input signal, can lead to more accurate and far more relaxed estimates for clock jitter requirements, in the example shown by more than two orders of magnitude. Actually, jitter requirements for the clock of a sampler-based receiver are quite close to the requirements for the LO in a mixing receiver, as will be clear when they are compared in section 3.4.

#### 2.2.4 SFDR

Due to various non-linear effects, the output of ADCs contain more signals than those present at the input. These are called spurious signals, or spurii.

These spurious signals should not exceed a certain level in order not to interfere with demodulation of the wanted signal. Derivation of this maximum allowed level requires knowledge of the minimum sensitivity level, of the demodulation algorithm and of the requirements on the output data of the demodulator. Unfortunately, for most demodulation algorithms only analyses or simulations with additive white gaussian

```

sample rate = 11.45 \text{ GHz}

SNR = 66 \text{ dB (11 bits)}

SFDR = 91 \text{ dB}

= 60 \text{ dB} = 60 \text{ dB} = 60 \text{ dB} = 60 \text{ dB} = 60 \text{ dB} = 60 \text{ dB} = 60 \text{ dB} = 60 \text{ dB} = 60 \text{ dB} = 60 \text{ dB} = 60 \text{ dB} = 60 \text{ dB} = 60 \text{ dB} = 60 \text{ dB} = 60 \text{ dB} = 60 \text{ dB} = 60 \text{ dB} = 60 \text{ dB} = 60 \text{ dB} = 60 \text{ dB} = 60 \text{ dB} = 60 \text{ dB} = 60 \text{ dB} = 60 \text{ dB} = 60 \text{ dB} = 60 \text{ dB} = 60 \text{ dB} = 60 \text{ dB} = 60 \text{ dB} = 60 \text{ dB} = 60 \text{ dB} = 60 \text{ dB} = 60 \text{ dB} = 60 \text{ dB} = 60 \text{ dB} = 60 \text{ dB} = 60 \text{ dB} = 60 \text{ dB} = 60 \text{ dB} = 60 \text{ dB} = 60 \text{ dB} = 60 \text{ dB} = 60 \text{ dB} = 60 \text{ dB} = 60 \text{ dB} = 60 \text{ dB} = 60 \text{ dB} = 60 \text{ dB} = 60 \text{ dB} = 60 \text{ dB} = 60 \text{ dB} = 60 \text{ dB} = 60 \text{ dB} = 60 \text{ dB} = 60 \text{ dB} = 60 \text{ dB} = 60 \text{ dB} = 60 \text{ dB} = 60 \text{ dB} = 60 \text{ dB} = 60 \text{ dB} = 60 \text{ dB} = 60 \text{ dB} = 60 \text{ dB} = 60 \text{ dB} = 60 \text{ dB} = 60 \text{ dB} = 60 \text{ dB} = 60 \text{ dB} = 60 \text{ dB} = 60 \text{ dB} = 60 \text{ dB} = 60 \text{ dB} = 60 \text{ dB} = 60 \text{ dB} = 60 \text{ dB} = 60 \text{ dB} = 60 \text{ dB} = 60 \text{ dB} = 60 \text{ dB} = 60 \text{ dB} = 60 \text{ dB} = 60 \text{ dB} = 60 \text{ dB} = 60 \text{ dB} = 60 \text{ dB} = 60 \text{ dB} = 60 \text{ dB} = 60 \text{ dB} = 60 \text{ dB} = 60 \text{ dB} = 60 \text{ dB} = 60 \text{ dB} = 60 \text{ dB} = 60 \text{ dB} = 60 \text{ dB} = 60 \text{ dB} = 60 \text{ dB} = 60 \text{ dB} = 60 \text{ dB} = 60 \text{ dB} = 60 \text{ dB} = 60 \text{ dB} = 60 \text{ dB} = 60 \text{ dB} = 60 \text{ dB} = 60 \text{ dB} = 60 \text{ dB} = 60 \text{ dB} = 60 \text{ dB} = 60 \text{ dB} = 60 \text{ dB} = 60 \text{ dB} = 60 \text{ dB} = 60 \text{ dB} = 60 \text{ dB} = 60 \text{ dB} = 60 \text{ dB} = 60 \text{ dB} = 60 \text{ dB} = 60 \text{ dB} = 60 \text{ dB} = 60 \text{ dB} = 60 \text{ dB} = 60 \text{ dB} = 60 \text{ dB} = 60 \text{ dB} = 60 \text{ dB} = 60 \text{ dB} = 60 \text{ dB} = 60 \text{ dB} = 60 \text{ dB} = 60 \text{ dB} = 60 \text{ dB} = 60 \text{ dB} = 60 \text{ dB} = 60 \text{ dB} = 60 \text{ dB} = 60 \text{ dB} = 60 \text{ dB} = 60

```

Table 2.2: summary of ADC requirements in a combined Bluetooth and Hiperlan/2 software radio receiver

noise are known from the literature. Therefore, ideally some simulations of the demodulation algorithm with harmonic interferers are performed.

The ratio of the single-tone amplitude to the largest spurious signal is called the spurious free dynamic range (SFDR). As with the SNR requirement, the input signal is equal to the maximum blocker signal within the filter bandwidth.

#### Example

As with the SNR requirement, the maximum input signal during blocker tests is 0 dBm for Hiperlan/2 en -10 dBm for Bluetooth.

Unfortunately, no data is available for the maximum level of harmonic interfering signals. Therefore, the same levels are taken as for the maximum in-band noise. These are shown in table 2.1 (fourth column) on page 11.

For Bluetooth, during blocker tests the wanted signal is 3 dB over the reference sensitivity level. For Hiperlan/2, the level of the wanted signal during blocking tests is unspecified, so a level of 3 dB over the sensitivity level is assumed as well. Therefore, the combined power of in-band noise+interferer can be 3 dB higher than that of the noise alone, and the power of the in-band interferer can be exactly the same as that of the in-band noise as shown in table 2.1.

As the maximum input signal is 0 dBm and the maximum in-band interferer level is -91.2 dBm, the required SFDR is 91.2 dB.

#### 2.3 Feasibility

The requirements, derived in the previous section, are summarised in table 2.2.

To assess the feasibility of a Software Radio, it it not only necessary to know the requirements on the receiver (mainly the ADC), but also the performance that is actually achieved by currently available converters. Several overviews of available ADCs exist, notably [28], (later summarised in [29]), but they are all more than five years old, and much progress has been made in the mean time. However, it is clear from looking at more recent publications that just the combination of sample rate and SNR is not presently feasible. For instance, a state-of-the-art ADC such as the one presented in [30] achieves an SNR of 48 dB and an SFDR of 65 dB at a sample rate of 1.35 GHz.

Even though such an ADC is not yet feasible, we can estimate the power that such an ADC would consume by extrapolating from existing designs. This is done using a commonly used figure of merit (FoM) for ADCs:

$$FoM = \frac{P_{diss}}{2^{SNR_{bits}} f_s}$$

(2.12)

Extrapolating from the same state-of-the-art ADC as mentioned above [30], which achieves a FoM of 0.6 pJ/conversion step, the required ADC for our software radio would consume FoM  $\cdot 2^{SNR_{bits}} \cdot f_s = 0.6 \cdot 10^{-12} \cdot 2^{11} \cdot 11.45 \cdot 10^9 = 14$  W. Therefore, even if this ADC would exist, its power consumption would be prohibitive for mobile applications.

#### 2.4 Summary and Conclusions

The requirements for software radio receiver front-ends were derived, and these requirements were calculated for a receiver for two different standards. From this, it can be concluded that at present, software radio is not feasible.

Software radio however, is only one possible architecture to obtain a flexible radio receiver. The next chapter will discuss a different one.

## Chapter 3

## **Software Defined Radio**

The previous chapter presented the software radio concept, and concluded that due to constraints in the presently available technology, it is infeasible at the moment.

This was mainly caused by requirements on the ADC. Therefore, a different architecture has to be found. An ADC is still needed because the information has to be available digitally, but the requirements on it can be lowered by filtering. This lowers the dynamic range of the input signal by attenuating strong interferers, and lowers the bandwidth, leading to a lower sample rate requirement. Downconversion is employed as well, because narrowband filters are more easily accomplished at lower frequencies, and because lowpass ADCs avoid many of the problems associated with bandpass ADCs.

Because downconversion and filtering are in part performed by analogue hardware, less functionality will be implemented in software. Despite this, software can still define the functionality of the receiver, hence the name 'software defined radio'.

In this chapter, several downconversion architectures are discussed. First, the requirements for a downconverter without RF pre-filtering are derived. Then, the same requirements are derived for a downconverter with a pre-filter. This is done for filters of different bandwidths an filter orders, to show the trade-off between the requirements of the filter and of the rest of the receiver. After deriving the requirements, some other aspects of downconversion receivers are discussed.

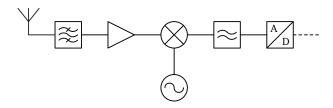

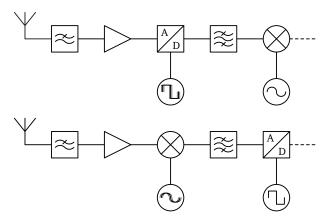

Figure 3.1: A superheterodyne receiver

#### 3.1 Downconverter without RF pre-filtering

A more traditional approach to downconversion is the superheterodyne receiver of figure 3.1. Incoming radio signals are first amplified by the low noise amplifier (LNA). The mixer then multiplies them with the LO signal. This corresponds to a convolution with a dirac delta in the frequency domain, i.e. a frequency shift. The downconverted signal is then filtered, and converted to a digital signal. Further filtering and demodulation is performed digitally.

This section presents the requirements for this type of receiver.

#### 3.1.1 Noise requirement

For the software radio receiver in the previous chapter, noise was considered (together with the maximum signal level) as part of the SNR requirement (section 2.2.2). For a more traditional radio receiver however, these parameters are treated separately, and thus noise figure (NF) is a more commonly used parameter.

Noise figure is the difference between the SNR of the output signal and the SNR of the input signal. The input SNR can be calculated from the minimum power level of the input signal, often called the input sensitivity, and the thermal noise within the input bandwidth.

The required output SNR depends on the required bit error rate and on the demodulator. As in section 2.2.2, numbers for this are taken from the literature.

#### **Example**

Again, the combined Bluetooth / Hiperlan/2 receiver is used as an example. The input SNR (fourth column) is the difference between the minimum input power (second column in table 3.1) and the thermal

|                | required    | in-band   | input | required | max. |

|----------------|-------------|-----------|-------|----------|------|

|                | sensitivity | th. noise | SNR   | SNR      | NF   |

| standard       | (dBm)       | (dBm)     | (dB)  | (dB)     | (dB) |

| HL/2 (6 Mb/s)  | -85         | -101.8    | 16.8  | 6.2      | 10.6 |

| HL/2 (9 Mb/s)  | -83         | -101.8    | 18.8  | 7.4      | 11.4 |

| HL/2 (12 Mb/s) | -81         | -101.8    | 20.8  | 8.9      | 11.9 |

| HL/2 (18 Mb/s) | -79         | -101.8    | 22.8  | 10.9     | 11.9 |

| HL/2 (27 Mb/s) | -75         | -101.8    | 26.8  | 14.5     | 12.3 |

| HL/2 (36 Mb/s) | -73         | -101.8    | 28.8  | 17.0     | 11.8 |

| HL/2 (54 Mb/s) | -68         | -101.8    | 33.8  | 22.3     | 11.7 |

|                |             |           |       |          |      |

| Bluetooth      | -70         | -113.9    | 43.9  | 18.0     | 25.9 |

Table 3.1: Calculation of the maximum noise figure of the combined receiver, for all (sub-)standards. (Hiperlan/2 is abbreviated here as HL/2)

noise in the input bandwidth (third column). The output SNR required for demodulation (again taken from [2]) is shown in the fifth column. This is subtracted from the input SNR, resulting in the required noise figure (sixth column).

This shows that the required noise figure for the combined Hiperlan/2 and Bluetooth receiver is 10.6 dB.

#### 3.1.2 Linearity requirement

When only the wanted signal is present at the input, non-linearity usually has no ill effects. However, when other signals are present as well, through non-linearity these signals can interfer with the wanted signal.

As with the software radio of the previous chapter, the linearity requirements depend on the signal level of the interferers, and on the maximum allowed level of in-band interference. Because numbers for the maximum allowed level of in-band interference are hard to obtain, instead the same levels are taken as for the maximum in-band noise, as was done in section 2.2.4.

This section discusses various non-linear effects and their corresponding requirements.

#### Harmonic distortion

Harmonic distortion of an interferer at frequency  $f_i$  leads to products at  $n \cdot f_i$ ,  $\forall n \ge 2$ . Conversely, a wanted signal at frequency  $f_w$  is susceptible to harmonic distortion products of interferers at frequencies  $\frac{1}{n}f_w$ .

In single-band receivers, interferers at half the frequency of the wanted signal or lower, have been attenuated significantly by the band filter between the antenna and the LNA. Therefore, in these receivers harmonic distortion is usually not a problem.

In wide-band receivers however, it can be a problem. To calculate the maximum harmonic distortion, first the power levels of the interfering signals have to be known. These are taken from the blocker spectra, at the frequencies  $\frac{1}{n}f_w$ .

Also, the maximum level of distortion products that is allowed by the demodulator has to be known. As discussed in section 2.2.4, these are hard to obtain, and again maximum noise levels are used instead.

From these numbers, maximum levels for harmonic distortion could be calculated. This is not done here, because intermodulation already limits the feasibility of the architectures of this section, as will be shown later.

#### Second order intermodulation

Intermodulation requires two interfering signals. Taking two harmonic input signals at frequencies  $f_{i,1}$  and  $f_{i,2}$ , then (with  $\phi_{i,1} = 2\pi f_{i,1}t$  and  $\phi_{i,2} = 2\pi f_{i,2}t$ ):

$$\left(\sin\phi_{i,1} + \sin\phi_{i,2}\right)^2 = \sin^2\phi_{i,1} + 2\sin\phi_{i,1}\sin\phi_{i,2} + \sin^2\phi_{i,2}$$

$$= 1 - \frac{1}{2}\cos 2\phi_{i,1} + \cos(\phi_{i,1} - \phi_{i,2}) - \cos(\phi_{i,1} + \phi_{i,2}) - \frac{1}{2}\cos 2\phi_{i,2}$$

(3.1)

The terms printed in bold are due to intermodulation. Hence, the second order intermodulation products are at frequencies  $f_{i,1} + f_{i,2}$  and  $|f_{i,1} - f_{i,2}|$ .

This means that if one of the interferers is close in frequency to the wanted signal, the other has to be at double that frequency, or at a very low frequency. Therefore, at least one of the two signals is separated far from the wanted signal, In a single-band receiver, that signal has been attenuated by the band filter and second order intermodulation

is usually not a problem. In wide-band receivers however, it can be a problem.

The measure used for second order distortion is the second order input-referred intercept point ( $IIP_2$ ). This is the input power at which (extrapolated)  $2^{nd}$  order intermodulation products reach the same output power as does the wanted signal.

To derive the  $IIP_2$  requirement, the level of the interferers has to be known, as well as the maximum in-band interference allowed by the demodulator. The required  $IIP_2$  can be calculated with

$$P_{IIP_2} = \frac{{P_i}^2}{P_{max.in-band}}$$

Here,  $P_i$  is the input power of the two unwanted signals (usually assumed to be equal) and  $P_{max,in-band}$  is the maximum allowed input-referred in-band interference. As the powers of the two unwanted signals are not necessarily equal, the equivalence forumula A.4 derived in appendix A.2 is applied:

$$P_{IIP_2} = \frac{P_{i,1}P_{i,2}}{P_{max,in-band}}$$

There is an infinite number of combinations of  $f_{i,1}$  and  $f_{i,2}$  that leads to second order intermodulation products at  $f_w$ . This is solved by sweeping  $f_{i,1}$  over the whole frequency range over which the blocker profile is defined, and for each  $f_{i,1}$  calculating the two values for  $f_{i,2}$ , that result in an intermodulation product at  $f_w$ .

From all these combinations, the one that leads to the highest  ${\rm IIP}_2$  requirement is selected.

#### Example

Previous linearity requirements were based on only one interferer, but for intermodulation, two are necessary. However, the only requirements from the Bluetooth [3] and Hiperlan/2 [4] standards with out-of-band interferers is the blocker spec, which includes only one interferer. For the design of a single-band receiver this is not of great consequence, since out-of-band interferers are attenuated by the RF filter and this attenuation has a more than linear effect on intermodulation products (quadratic for IM2, cubic for IM3).

In a wideband receiver on the other hand, these interferers are not attenuated. Therefore, assuming two interferers can be present as well, intermodulation distortion can have more effect. For the combined receiver for Bluetooth and Hiperlan/2, the  $IIP_2$  is calculated from the blocker profile, using the maximisation procedure outlined above.

For Bluetooth, the minimum  ${\rm IIP_2}$  is determined by two input signals that are both at -10 dBm. Many combinations of frequencies exist that give an intermodulation product in the Bluetooth band, and where the blocker level is -10 dBm. For example, two interferers at 500 and 1950 MHz intermodulate to 2450 MHz. With two interferers at -10 dBm and a maximum in-band noise level of -88 dBm, the minimum  ${\rm IIP_2}$  is 68 dBm.

For Hiperlan/2, the minimum  $IIP_2$  is determined by two input signals at -10 and 0 dBm. These are for instance present at 750 MHz and 4500 MHz, intermodulating to 5250 MHz. With a maximum in-band noise level of -91 dBm, this gives a minimum  $IIP_2$  of 81 dBm.

Therefore, the combined receiver has an IIP<sub>2</sub> requirement of 81 dBm.

#### Third order intermodulation

With two input signals at frequencies  $f_{i,1}$  and  $f_{i,2}$ , third order distortion leads to intermodulation products at  $2f_{i,1}+f_{i,2}$ ,  $f_{i,1}+2f_{i,2}$ ,  $|2f_{i,1}-f_{i,2}|$  and  $|f_{i,1}-2f_{i,2}|$ , as can be seen from the following equation.

$$\left(\sin\phi_{i,1} + \sin\phi_{i,2}\right)^{3}$$

$$= \sin^{3}\phi_{i,1} + 3\sin^{2}\phi_{i,1}\sin\phi_{i,2} + 3\sin\phi_{i,1}\sin^{2}\phi_{i,2} + \sin^{3}\phi_{i,2}$$

$$= \frac{3}{4}\sin\phi_{i,1} - \frac{1}{4}\sin3\phi_{i,1} + \frac{3}{2}\sin\phi_{i,2} - \frac{3}{4}\sin(\phi_{i,2} - 2\phi_{i,1}) - \frac{3}{4}\sin(\phi_{i,2} + 2\phi_{i,1}) + \frac{3}{2}\sin\phi_{i,1} - \frac{3}{4}\sin(\phi_{i,1} - 2\phi_{i,2}) - \frac{3}{4}\sin(\phi_{i,1} + 2\phi_{i,2}) + \frac{3}{4}\sin\phi_{i,2} - \frac{1}{4}\sin3\phi_{i,2}$$

$$(3.2)$$

The four terms due to intermodulation are printed in bold. By reasoning analogous to that in the previous two sections, the second and last of those four terms are usually irrelevant in single-band receivers. The other two however, are relevant.

In wide-band receivers, all four terms can be a problem. Selecting the combination of two interfering signals that intermodulate to the wanted frequency is done analogous to the procedure in the previous

section, except that now for every  $f_{i,1}$  there are four possible frequencies  $f_{i,2}$  that lead to an intermodulation product at  $f_w$ .

The required IIP<sub>3</sub> can be calculated with:

$$P_{IIP_3} = \frac{P_i \sqrt{P_i}}{\sqrt{P_{max,in-band}}}$$

As before,  $P_i$  is the input power of the unwanted signals and  $P_{max,in-band}$  is the maximum allowed input-referred in-band interference. As the powers of the two unwanted signals are not necessarily equal, the equivalence forumula A.5 is applied:

$$P_{IIP_3} = \frac{\sqrt{P_{i,1}^2 P_{i,2}}}{\sqrt{P_{max,in-band}}}$$

or, for intermodulation products at  $|2f_{i,2} - f_{i,1}|$  or  $2f_{i,2} + f_{i,1}$ :

$$P_{IIP_3} = \frac{\sqrt{P_{i,1}P_{i,2}^2}}{\sqrt{P_{max,in-band}}}$$

#### Example

The  $IIP_3$  is calculated using the same maximisation procedure as was used for  $IIP_2$ . For Bluetooth this resulted in an  $IIP_3$  requirement of 29 dBm. This number was determined by two -10 dBm signals at for instance 750 and 950 MHz intermodulating to 2450 MHz. For Hiperlan/2, two 0 dBm signals at for instance 1500 and 2250 MHz intermodulate to 5250 MHz. These numbers lead to a minimum  $IIP_3$  of 45.5 dBm. Therefore, the  $IIP_3$  requirement for the combined receiver is 45.5 dbm.

#### Compression

Because the output power of an amplifier is limited, gain will drop for increasing input signals. Therefore, in the presence of strong input signals, the wanted signal will also have lower amplification, and sensitivity will drop. This phenomenon is called compression or desensitisation.

In single-band receivers, strong out-of-band interferers are usually attenuated by a filter. However, in a multi-band receiver this is not the case and those interferers will cause desensitisation.

| noise figure     | 10.6 dB  |

|------------------|----------|

| $IIP_2$          | 81 dBm   |

| $IIP_3$          | 45.5 dBm |

| 3-dB compression | 0 dBm    |

Table 3.2: summary of downconverter requirements in a combined Bluetooth and Hiperlan/2 software define radio receiver without an RF pre-filter

#### **Example**

For Bluetooth, absent a blocker, a wanted signal at the sensitivity level has to be decoded with a certain bit error rate. In the presence of a blocker, a wanted signal at 3 dB over this sensitivity level has to be decoded at the same bit error rate. The maximum blocker level is -10 dBm [3, part A, sec. 4.3].

Therefore, with the blocker present, the wanted signal can be attenuated by 3 dB, so the -3-dB compression point should be -10 dBm for Bluetooth reception.

For Hiperlan/2, a similar analysis holds, except the maximum blocker level is 0 dBm.

Therefore, the combined reception needs a 3-dB compression point of at level 0 dBm.

#### 3.1.3 Conclusion

This section presented various requirements on a wideband downconverter without RF pre-filtering. Table 3.2 shows a summary of these requirements.

Many downconverters exist with a noise figure of less than 10.6 dB. However, the author is not aware of any published downconverters that come close to meeting the presented linearity requirements. Another problem with this type of receiver would be harmonic mixing: signals around harmonics of the LO will also be downconverted.

Therefore, a different architecture will be discussed in the next section.

Figure 3.2: A superheterodyne receiver with RF bandpass filter

## 3.2 Downconverter with RF pre-filtering

The major shortcoming of the architecture in the previous section is the high linearity requirement on the receiver. These requirements can be relaxed by adding a bandpass filter in front of the receiver, as shown in figure 3.2.

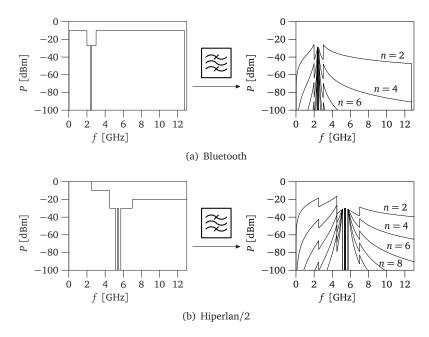

The blocker spectrum seen in figure 2.5 on page 18 poses an upper limit to the unwanted signals. When pre-filtering is used, the power transfer of the filter can easily be applied to the blocker spectrum to arrive at the equivalent blocker spectrum. This is illustrated in figure 3.3.

As can be seen in this figure, filtering lowers the maximum signal present at the input of the downconverter. A 6<sup>th</sup> order filter with a relatively high bandwidth (1-dB points at the band edges) already attenuates out-of-band blockers to the same level as in-band signals. One could therefore expect this to lower linearity requirements to levels comparable to single-band receivers. To verify this, the rest of this section presents the linearity requirements depending on filter parameters.

#### 3.2.1 Linearity requirement

Strong out-of-band interferers imposed very high linearity requirements on the filterless downconverter of the previous section. Using a filter, these out-of-band signals are attenuated, so the linearity requirements on the receiver front-end should be lower.

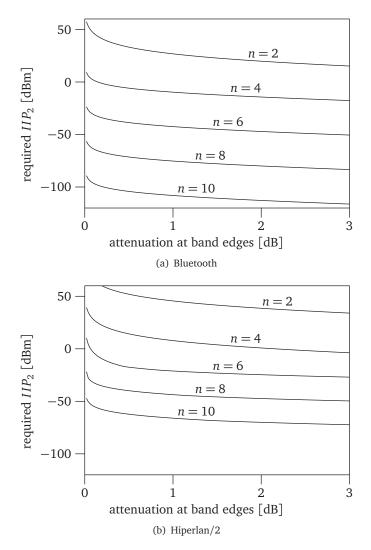

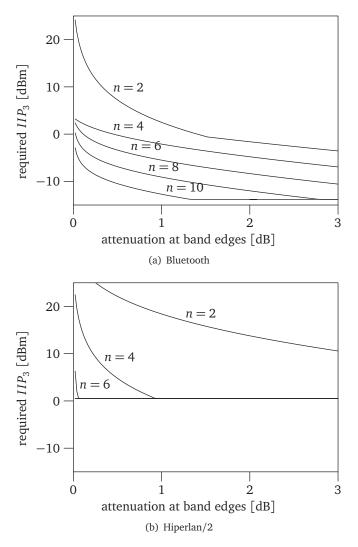

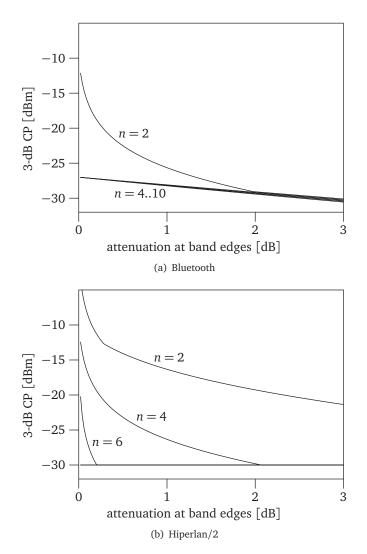

To see how much lower, the procedure for assessing the various linearity requirements outlined in the previous section can be used again. The difference is that now the filtered blocker spectra are used. This is done for both standards and with several filter orders and filter bandwidths.

Figure 3.3: Effect of filtering on the blocker spectrum of Bluetooth and Hiperlan/2, using a Butterworth filter of order n=2, 4, 6, 8 or 10, with its -1 dB points at 2400 and 2483.5 MHz (Bluetooth band edges), and 5150 and 5725 MHz (Hiperlan/2 band edges).

All calculations are done using a Butterworth filter. Other filter types exist that achieve better steepness, but Butterworth filters are less dependent on component variations and therefore more reproducable. To facilitate a trade-off between filter attenuation and linearity requirements, the attenuation of the filter at the band edges has been varied, as well as the filter order.

In addition to the out-of-band interferers discussed above, the Bluetooth standard also specifies levels of in-band interferers for the purpose of setting odd-order intermodulation distortion requirements [3, section 4.4]. For this test, the wanted signal is at -64 dBm. With a minimum required SNR of 18 dB for demodulation (as before), this results in a maximum level for noise+interference of -82 dBm. With noise at -88 dBm, this allows a maximum interference level of -83.3 dBm. The power of the interferers is specified at -39 dBm. These numbers lead to

a minimum  ${\rm IIP_3}$  of -13.8 dBm. As these interferers are in-band, they are assumed to be independent of the RF pre-filter. Therefore, this level is taken as the minimum  ${\rm IIP_3}$  for Bluetooth. A comparable specification for Hiperlan/2 does not exist.

The results of these calculation are shown in figures 3.4 ( $IIP_2$ ) and 3.5 ( $IIP_3$ ).

In figure 3.6, the required 3-dB compression point for both Bluetooth and Hiperlan/2 are shown. Both are shown as a function of band-edge attenuation and filter order.

From figures 3.4, 3.5 and 3.6, it can be concluded that indeed the linearity requirements are lowered by filtering. Also, it can be seen that a 4<sup>th</sup> order filter with moderate band-edge attenuation (between 0.5 and 1 dB) yields feasible linearity requirements.

Of interest is the flat requirements for  $IIP_3$  and compression point for Hiperlan/2 reception, as indicated by the horizontal lines in figures 3.5b and 3.6b. These are due to the filter passing both Hiperlan/2 subbands, plus the frequency range between them. Therefore, interferers in-between those sub-bands are not attenuated, independent of filter width.

To gain more insight into the blockers that determine the requirements shown in this section, tables 3.3, 3.4 and 3.5 are provided. These tables show the frequency and the level of the 'worst-case' blockers, i.e. those that determine the requirements. This is only done for filters with a band edge attenuation of 0.5 dB.

The figures in this section all use the attenuation at the band edges as a parameter. As this attenuation directly adds to the required noise figure, this is an important parameter that can be used when making a trade-off between the required noise figure and linearity.

Another factor to consider is the feasibility of the filter. To assess this, the filter Q is more often used as a parameter. To relate this to the band-edge attenuation, table 3.6 is provided.

### 3.2.2 Selection of intermediate frequency

Until here, the frequency of the local oscillator and the intermediate frequency (IF) have not been discussed. Several options exist for this.

The main impact this has is on the method to suppress image signals. Image signals have the same frequency difference to the LO signal as the wanted signal, but are 'on its other side'. They are converted to the same frequency as the wanted signal, and thus lead to interference.

Figure 3.4: required  $IIP_2$  vs. band-edge attenuation for Butterworth filters of order n.

Figure 3.5: required  $IIP_3$  vs. band-edge attenuation for Butterworth filters of order n.

Figure 3.6: required 3-dB compression point vs. band-edge attenuation for Butterworth filters of order n.

| n  | $f_1$ [GHz] | P <sub>in</sub> @f <sub>1</sub><br>[dBm] | A@f <sub>1</sub><br>[dB] | P <sub>out</sub> @f <sub>1</sub><br>[dBm] | $f_2$ [GHz] | P <sub>in</sub> @f <sub>2</sub><br>[dBm] | A@f <sub>2</sub><br>[dB] | P <sub>out</sub> @f <sub>2</sub><br>[dBm] | IIP <sub>2</sub><br>[dBm] |

|----|-------------|------------------------------------------|--------------------------|-------------------------------------------|-------------|------------------------------------------|--------------------------|-------------------------------------------|---------------------------|

| 0  | 0.500       | -10.0                                    | 0.0                      | -10.0                                     | 1.950       | -10.0                                    | 0.0                      | -10.0                                     | 68.0                      |

| 2  | 2.000       | -10.0                                    | 12.5                     | -22.5                                     | 4.450       | -10.0                                    | 22.3                     | -32.3                                     | 33.2                      |

| 4  | 2.399       | -27.0                                    | 0.5                      | -27.5                                     | 4.849       | -10.0                                    | 56.3                     | -66.3                                     | -5.9                      |

| 6  | 2.399       | -27.0                                    | 0.6                      | -27.6                                     | 4.849       | -10.0                                    | 89.1                     | -99.1                                     | -38.7                     |

| 8  | 2.399       | -27.0                                    | 0.6                      | -27.6                                     | 4.849       | -10.0                                    | 121.8                    | -131.8                                    | -71.4                     |

| 10 | 2.399       | -27.0                                    | 0.6                      | -27.6                                     | 4.849       | -10.0                                    | 154.6                    | -164.6                                    | -104.2                    |

|    |             |                                          |                          | (a) E                                     | Bluetooth   |                                          |                          |                                           |                           |

|    |             |                                          |                          |                                           |             |                                          |                          |                                           |                           |

|    | $f_1$       | $P_{in}@f_1$                             | $A@f_1$                  | $P_{out}@f_1$                             | $f_2$       | $P_{in}@f_2$                             | $A@f_2$                  | Pout@f2                                   | $IIP_2$                   |

| n  | [GHz]       | [dBm]                                    | [dB]                     | [dBm]                                     | [GHz]       | [dBm]                                    | [dB]                     | [dBm]                                     | [dBm]                     |

| 0  | 0.750       | 0.0                                      | 0.0                      | 0.0                                       | 4.500       | -10.0                                    | 0.0                      | -10.0                                     | 81.0                      |

| 2  | 2.500       | 0.0                                      | 15.2                     | -15.2                                     | 2.750       | -10.0                                    | 13.9                     | -23.9                                     | 51.9                      |

| 4  | 4.500       | -10.0                                    | 13.2                     | -23.2                                     | 9.750       | -20.0                                    | 33.6                     | -53.6                                     | 14.2                      |

| 6  | 5.150       | -30.0                                    | 0.5                      | -30.5                                     | 10.400      | -20.0                                    | 58.0                     | -78.0                                     | -17.5                     |

| 8  | 5.150       | -30.0                                    | 0.5                      | -30.5                                     | 10.400      | -20.0                                    | 80.4                     | -100.4                                    | -39.9                     |

| 10 | 5.150       | -30.0                                    | 0.5                      | -30.5                                     | 10.400      | -20.0                                    | 102.8                    | -122.8                                    | -62.3                     |

|    |             |                                          |                          | (b) H                                     | Iiperlan/2  |                                          |                          |                                           |                           |

Table 3.3: An overview of the interferers that determine  $IIP_2$ , using filters with a band edge attenuation of 0.5 dB and varying order. This corresponds to the results shown in figure 3.4 at 0.5 dB.

#### High IF

In a conventional superheterodyne receiver, the problem of image signals is solved using an image reject filter. A filter was already needed for relaxing the front-end linearity requirements, but more filtering may be necessary.

One option for lowering the image filter requirement is chosing a very high IF. This is called upconversion and is generally considered a separate architecture. It is discussed in the next section.

Another problem with receivers that reject image signals using a filter, is that this filter is usually placed in front of the LNA. Therefore, noise generated by the LNA at the image frequency is not suppressed, and is subsequently converted to the IF frequency.

#### Upconversion

In an upconverting receiver, the IF is placed (much) higher than the input frequencies. This relaxes requirements on the image reject filter, up to the point that even in a wideband receiver, this filter does not

| n                | f <sub>1</sub><br>[GHz]                   | P <sub>in</sub> @f <sub>1</sub><br>[dBm] | A@f <sub>1</sub><br>[dB]   | P <sub>out</sub> @f <sub>1</sub><br>[dBm] | $f_2$ [GHz]                               | P <sub>in</sub> @f <sub>2</sub><br>[dBm] | A@f <sub>2</sub><br>「dB]          | P <sub>out</sub> @f <sub>2</sub><br>[dBm] | IIP <sub>3</sub><br>[dBm]           |

|------------------|-------------------------------------------|------------------------------------------|----------------------------|-------------------------------------------|-------------------------------------------|------------------------------------------|-----------------------------------|-------------------------------------------|-------------------------------------|

| 0                | 0.950                                     | -10.0                                    | 0.0                        | -10.0                                     | 0.750                                     | -10.0                                    | 0.0                               | -10.0                                     | 29.0                                |

| 2                | 3.550                                     | -10.0                                    | 17.9                       | -27.9                                     | 3.000                                     | -10.0                                    | 12.8                              | -22.8                                     | 7.2                                 |

| 4                | 2.348                                     | -27.0                                    | 6.3                        | -33.3                                     | 2.399                                     | -27.0                                    | 0.5                               | -27.5                                     | -0.2                                |

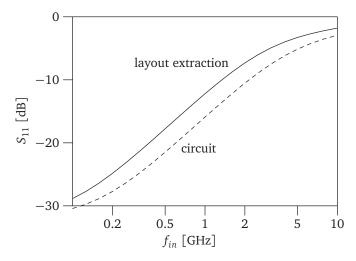

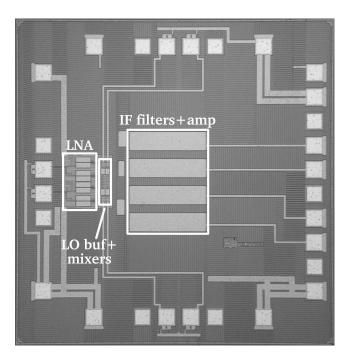

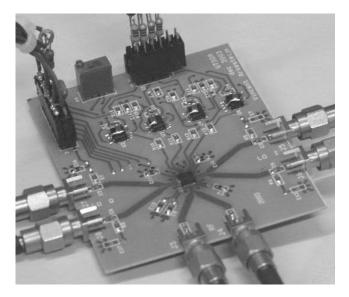

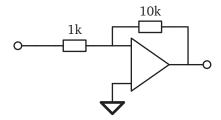

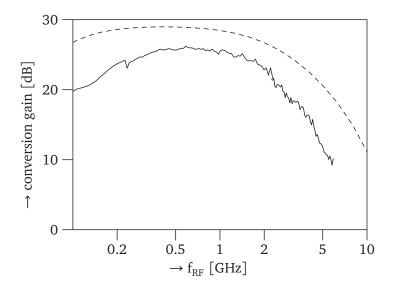

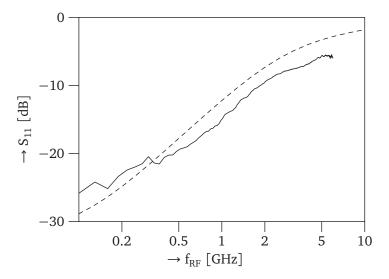

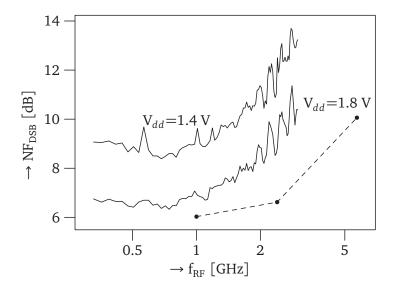

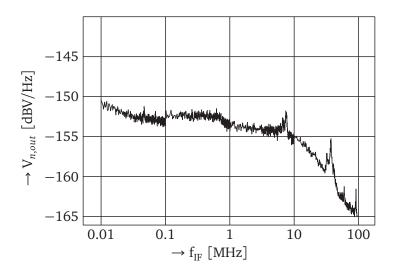

| 6                | 2.348                                     | -27.0                                    | 12.6                       | -39.6                                     | 2.399                                     | -27.0                                    | 0.6                               | -27.6                                     | -3.4                                |